# 1. Description

IN16C554A is an enhanced quadruple version of the 16C550UART (Universal Asynchronous Receiver Transmitter). IN16C554A is in part an upgrade version of IN16C554, as it is designed for 3.3V only and has AUTO-CTS, AUTO-RTS functions.

In IN16C554A, Each channel can be put into FIFO mode to relieve the CPU of excessive software overhead. In this mode, internal FIFOs are activated and 16 bytes plus 3 bit of error data per byte can be stored in both receive and transmit modes.

Each channel performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. The Status information includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions such as parity, overrun, framing, and break interrupt.

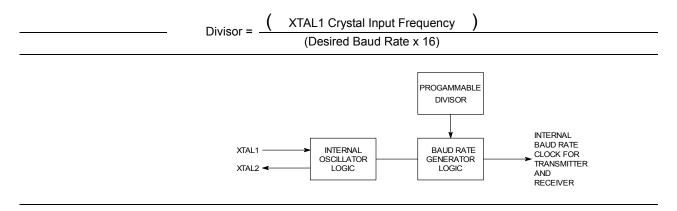

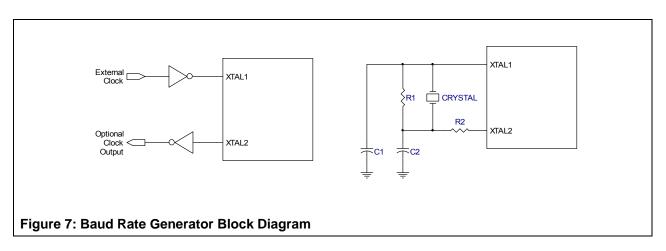

IN16C554A includes a programmable baud rate generator which is capable of dividing the timing reference clock input by divisors of 1 to 2<sup>16</sup>-1, and producing a 16x clock for driving the internal transmitter logic. Provisions are also included to use this clock to drive the receiver logic.IN16C554A has complete MODEM-control capability and an interrupt system that can be programmed to the user's requirements, minimizing the computing required to handle the communication links. Moreover IN16C554A can select hardware flow control. Hardware flow control significantly reduces software overhead and increases system efficiency.

# 2. Features

- In the FIFO mode, Each channel's transmitter and receiver is buffered with 16-byte FIFO to reduce the number of interrupts to CPU.

- Adds or deletes standard asynchronous communication bits (start, stop, parity) to or from the serial data.

- Holding Register and Shift Register eliminate need for precise synchronization between the CPU and serial data.

- Independently controlled transmit, receive, line status and data interrupts.

- Programmable Baud Rate Generators which allow division of any input reference clock by 1 to 2<sup>16</sup>-1 and generate an internal 16X clock.

- Independent receiver clock input Modem control functions (CTS#, RTS#, DSR#, DTR#, RI#, and DCD#).

- Fully programmable serial interface characteristics.

- 5-, 6-, 7-, or 8-bit characters

- Even-, Odd-, or No-Parity bit

1-, 1.5-, 2-Stop bit generation. (Like other general UARTs, IN16C554 checks only one stop bit, no matter how many they are)

- False start bit detection

- Generates or Detects Line Break

- Internal diagnostic capabilities : Loopback controls for communications link fault isolation.

- Full prioritized interrupt system controls

- Hardware (RTS#/CTS#) Flow Control

# 3. Ordering Information

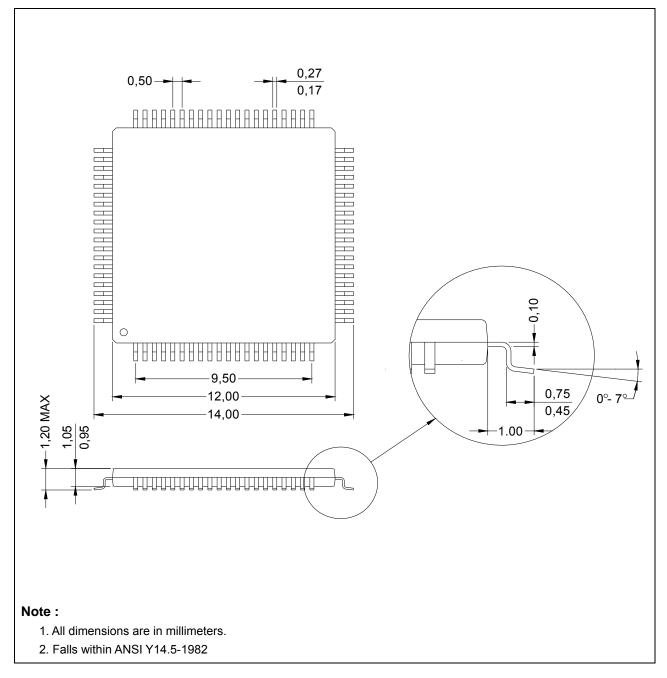

#### Table 1: Ordering Information

| Part Number    | Package     | Operating Temperature Range | Device Status |

|----------------|-------------|-----------------------------|---------------|

| IN16C554A-TQ80 | 80-Pin TQFP | -20 °C to +85 °C            | Active        |

| IN16C554A-PL68 | 68-Pin PLCC | -20 °C to +85 °C            | Active        |

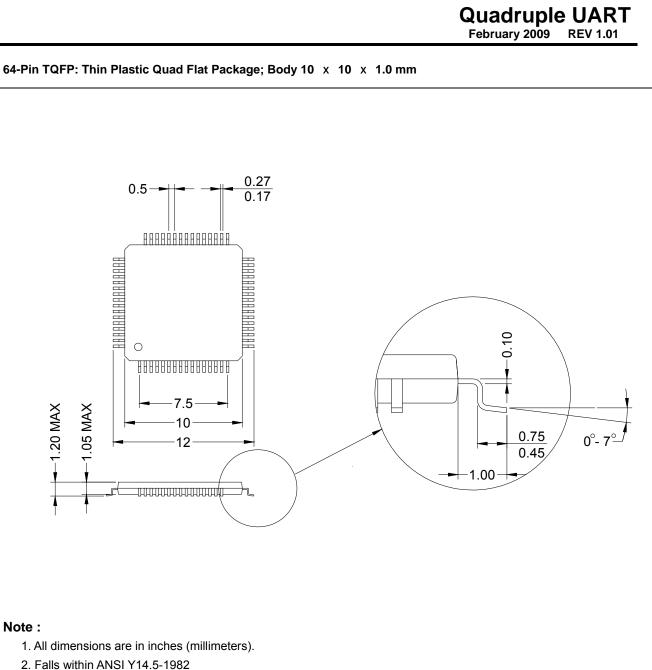

| IN16C554A-TQ64 | 64-Pin TQFP | -20 °C to +85 °C            | Active        |

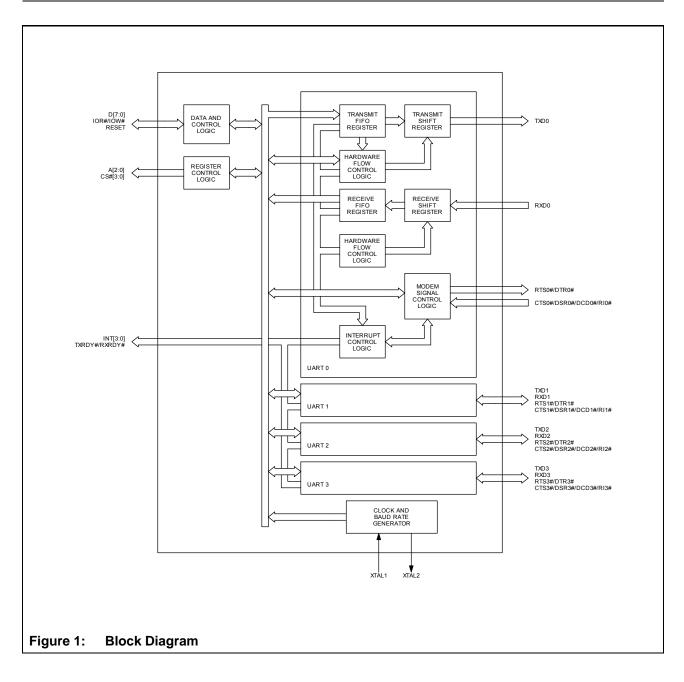

# 4. Block Diagram

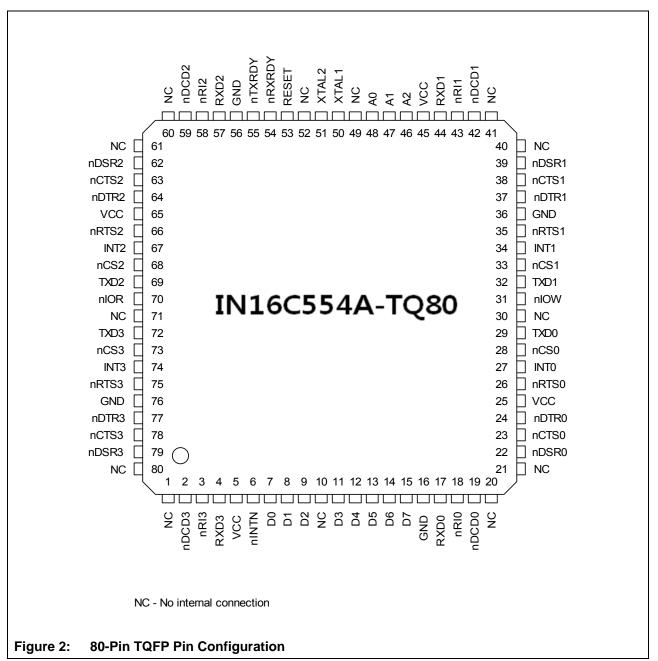

# 5. Pin Configuration

# 5.1 Pin Configuration for 80-Pin TQFP Package

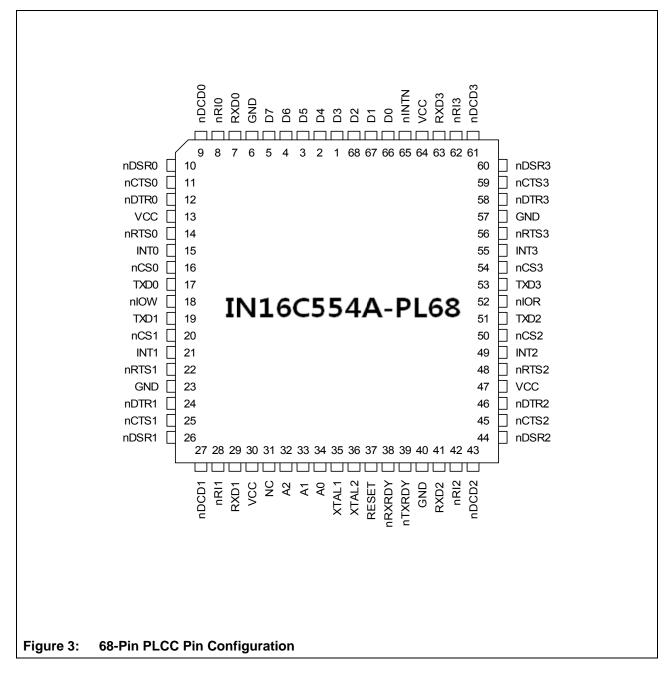

## 5.2 Pin Configuration for 68-Pin PLCC Package

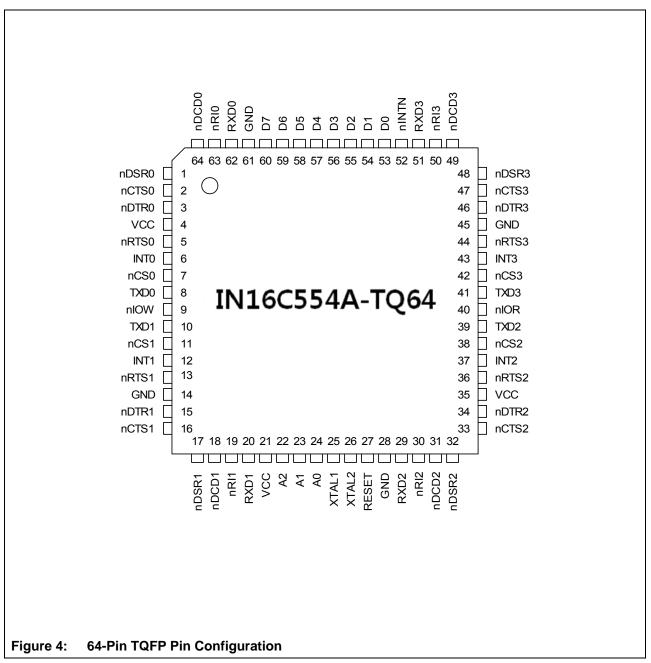

## 5.2 Pin Configuration for 64-pin-TQFP Package

# **5.3 Pin Description**

#### Table 2: Pin Description

| Data Bus Interface |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Туре                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| TQFP80             | PLCC68                                                                                                                                                                                                                                                           | TQFP64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 48                 | 34                                                                                                                                                                                                                                                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                                                                                             | Address Bus Lines [2:0]. These 3 address lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 47                 | 33                                                                                                                                                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                             | select one of the internal registers in UART channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 46                 | 32                                                                                                                                                                                                                                                               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                             | 0-3 during a data bus transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 7                  | 66                                                                                                                                                                                                                                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           | Data Bus Lines [7:0]. These pins are tri-state data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 8                  | 67                                                                                                                                                                                                                                                               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           | bus for data transfer to or from the controlling CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 9                  | 68                                                                                                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 11                 | 1                                                                                                                                                                                                                                                                | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 12                 | 2                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 13                 | 3                                                                                                                                                                                                                                                                | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 14                 | 4                                                                                                                                                                                                                                                                | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 15                 | 5                                                                                                                                                                                                                                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 70                 | 52                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                                                                                             | Read Data (active low strobe). A valid low level on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | IOR# will load the data of an internal register defined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | by address lines A [2:0] onto the UART data bus for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | access by an external CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 31                 | 18                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I                                                                                                                                             | Write Data (active low strobe). A valid low level on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | IOW# will transfer the data from external CPU to an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | internal register that is defined by address lines A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | [2:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 28                 | 16                                                                                                                                                                                                                                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I                                                                                                                                             | Chip Select 0, 1, 2, and 3 (active low). These pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 33                 | 20                                                                                                                                                                                                                                                               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                                                                                             | enable data transfers between the external CPU and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 68                 | 50                                                                                                                                                                                                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                                                                                             | the UART for the respective channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 73                 | 54                                                                                                                                                                                                                                                               | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 27                 | 15                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                             | External interrupt output. When activated, INTx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 34                 | 21                                                                                                                                                                                                                                                               | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                             | output informs CPU that                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 67                 | 49                                                                                                                                                                                                                                                               | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                             | UART has an interrupt to be serviced.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 74                 | 55                                                                                                                                                                                                                                                               | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 6                  | 65                                                                                                                                                                                                                                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                             | Interrupt Select. When INTSEL is left open or low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | state, the tri-state interrupts available on INT0-3 are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | enabled by MCR[3]. But, when INTSEL is in high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | state, INT0-3 are always enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

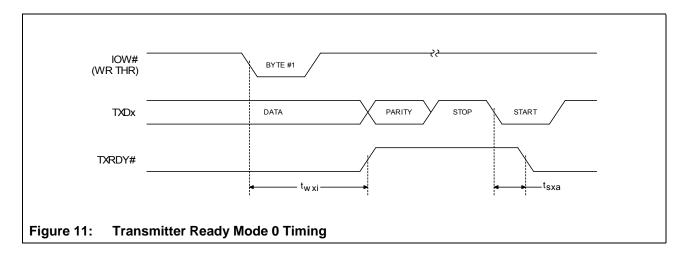

| 55                 | 39                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                             | Transmitter Ready (active low). This is asserted by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | TX FIFO/THR status for transmit channels 0-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

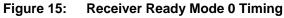

| 54                 | 38                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                             | Receiver Ready (active low). This is asserted by RX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               | FIFO/RHR status for receive channels 0-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | Pin         TQFP80         48         47         46         7         8         9         11         12         13         14         15         70         31         28         33         68         73         27         34         67         74         6 | Pin         TQFP80       PLCC68         48       34         47       33         46       32         7       66         8       67         9       68         11       1         12       2         13       3         14       4         15       5         70       52         70       52         31       18         28       16         33       20         68       50         73       54         27       15         34       21         67       49         74       55         6       65 | PinTQFP80PLCC68TQFP64483424473323463222766538675496855111561225713358144591556070524031189281673320116850387354422715634211267493774554363952 | Pin         Type           TQFP80         PLCC68         TQFP64         I           48         34         24         1           47         33         23         1           46         32         22         1           7         66         53         1/O           8         67         54         1/O           9         68         55         1/O           11         1         56         1/O           12         2         57         1/O           13         3         58         1/O           14         4         59         1/O           15         51         60         1/O           70         52         40         1           31         18         9         1           33         20         11         1           68         50         38         1           73         54         42         1           27         15         6         0           34         21         12         0           67         49         37         0 |  |  |  |

| Modem and Serial I/O Interface |        |        |        |      |                                                       |  |  |

|--------------------------------|--------|--------|--------|------|-------------------------------------------------------|--|--|

| Name                           | Pin    |        |        | Туре | Description                                           |  |  |

|                                | TQFP80 | PLCC68 | TQFP64 |      |                                                       |  |  |

| TXD0                           | 29     | 17     | 8      | 0    | Transmit Data. These pins are individual transmit     |  |  |

| TXD1                           | 32     | 19     | 10     | 0    | data output. During the local loop-back mode, the     |  |  |

| TXD2                           | 69     | 51     | 39     | 0    | TXD output pin is disabled and TXD data is            |  |  |

| TXD3                           | 72     | 53     | 41     | 0    | internally connected to the RXD input.                |  |  |

| RXD0                           | 17     | 7      | 62     | I    | Receive Data. These pins are individual receive data  |  |  |

| RXD1                           | 44     | 29     | 20     | 1    | input. During the local loop-back mode, the RXD       |  |  |

| RXD2                           | 57     | 41     | 29     | 1    | input pin is disabled and RXD data is internally      |  |  |

| RXD3                           | 4      | 63     | 51     | 1    | connected to the TXD output.                          |  |  |

| RTS0#                          | 26     | 14     | 5      | 0    | Request to Send (active low). These pins indicate     |  |  |